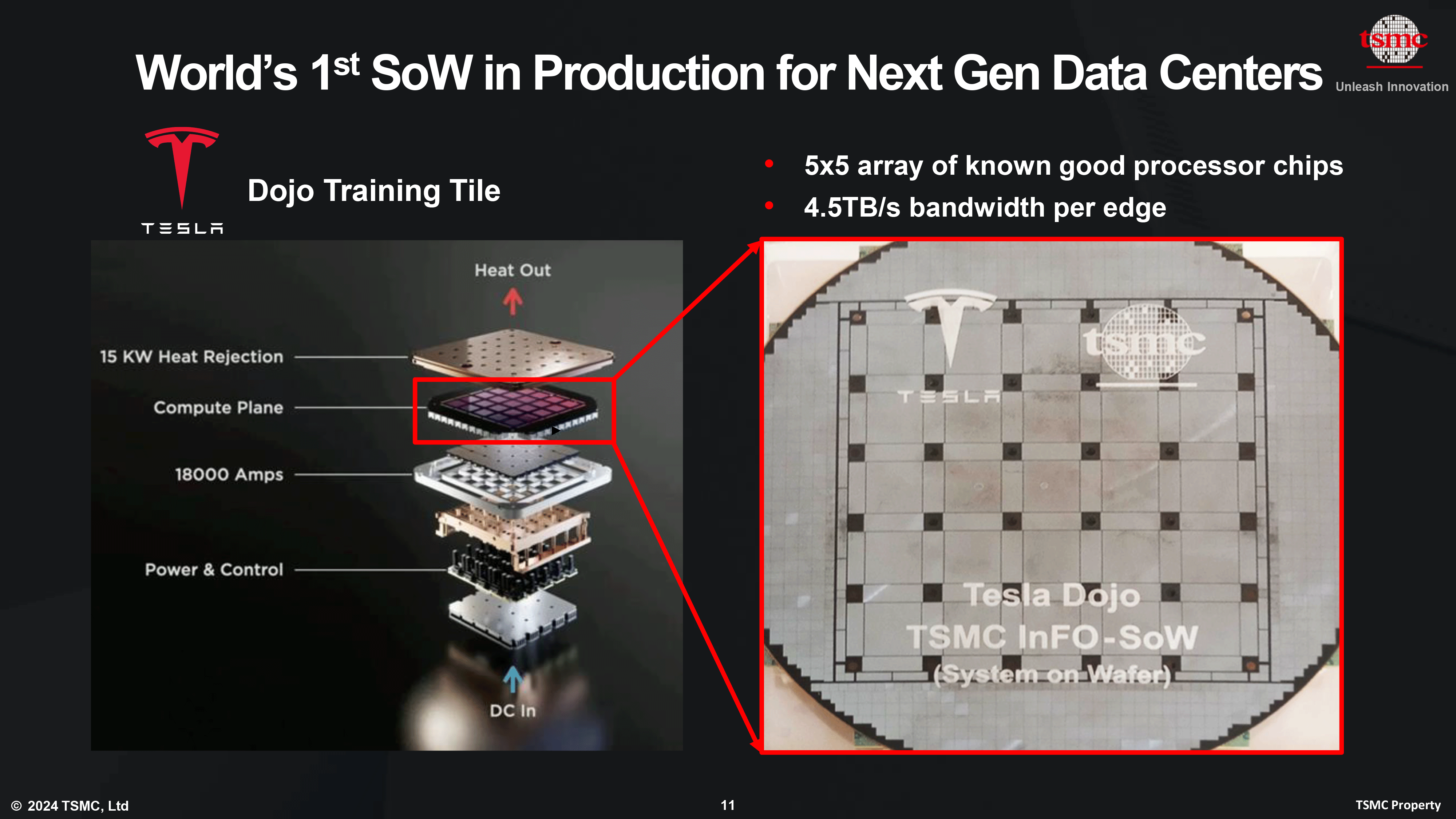

A TSMC está levando a batalha de fabricação em escala de wafer para a terceira dimensão com uma nova tecnologia. Em seu Simpósio de Tecnologia Norte-Americano, ela apresentou sua plataforma de sistema em wafer de próxima geração – CoW-SoW – que permitirá a integração 3D com projetos em escala de wafer. Isso se baseia na tecnologia de integração de sistema em wafer InFO_SoW que a TSMC introduziu em 2020, que permite construir processadores lógicos em escala de wafer. Até agora, apenas a Tesla adotou esta tecnologia para seu supercomputador Dojo, que a TSMC afirma estar agora em produção

Em sua próxima plataforma CoW-SoW, a TSMC deverá fundir dois de seus métodos de empacotamento – InFO_SoW e System on Integrated Chips (SoIC) – em sua plataforma system-on-wafer. Ao usar a tecnologia Chip-on-Wafer (CoW), este método permitirá o empilhamento de memória ou lógica diretamente sobre um sistema em wafer. Espera-se que a nova tecnologia CoW_SoW esteja pronta para produção em larga escala até 2027, embora ainda não se saiba quando os produtos reais chegarão ao mercado.

“Então, no futuro, usando integrações em nível de wafer [will allow] nossos clientes integrem ainda mais lógica e memória”, disse Kevin Zhang, vice-presidente de desenvolvimento de negócios da TSMC. “SoW não é mais uma ficção; isso é algo que já trabalhamos com nossos clientes [on] para produzir alguns dos produtos já existentes. Acreditamos que, ao aproveitar nossa avançada tecnologia de integração em nível de wafer, podemos fornecer aos nossos clientes um caminho muito importante que lhes permite continuar a aumentar sua capacidade de trazer mais computação, computação com maior eficiência energética, para seu cluster de IA ou [supercomputer].”

Atualmente, o CoW-SoW da TSMC se concentra na integração de processadores em escala wafer com memória HBM4. Essas pilhas de memória de próxima geração contarão com uma interface de 2.048 bits, o que tornará viável a integração do HBM4 diretamente sobre chips lógicos. Enquanto isso, também pode fazer sentido empilhar lógica adicional em processadores em escala wafer para otimizar custos.

Processadores em escala wafer em geral (ou seja, WSE da Cerebras) e processadores baseados em InFO_SoW em particular oferecem benefícios significativos de desempenho e eficiência, incluindo comunicações núcleo a núcleo de alta largura de banda e baixa latência, baixa impedância de rede de fornecimento de energia e alta eficiência energética. Como um bônus adicional, esses processadores também possuem redundância adicional na forma de núcleos “extras”.

Contudo, a tecnologia InFO_SoW tem certas limitações. Por exemplo, processadores em escala wafer feitos usando esse método dependem inteiramente de memória no chip, o que pode ser insuficiente para necessidades futuras de IA (mas é bom por enquanto). O CoW-SoW resolverá isso, pois permitirá colocar o HBM4 nesses wafers. Além disso, os wafers InFO_SoW são processados usando um único nó, e esse nó não suporta empilhamento 3D, que será suportado pelos produtos CoW-SoW.