TSMC divulgado as principais atualizações do roteiro para sua família de tecnologias de processo N3 (classe de 3 nanômetros) em seu Simpósio de Tecnologia Norte-Americano de 2023 esta semana. Como o nó final de alto desempenho da TSMC baseado em transistores FinFET, o N3 durará muitos anos e incluirá várias versões, incluindo N3P, uma redução óptica de aprimoramento de desempenho do N3E e N3X com foco no desempenho para aplicativos HPC que toleram alto vazamento e potência .

A produção em massa da TSMC em sua tecnologia de processo N3 (também conhecida como N3B) já está em andamento, mas esse nó usa litografia ultravioleta extrema em até 25 camadas e pode até usar padrão duplo EUV, o que o torna um nó particularmente caro de usar. Como resultado, a TSMC espera que a maioria de seus clientes use N3E, que pode usar EUV em até 19 camadas, não usa EUV de padrão duplo, tem uma janela de processo mais ampla e melhores rendimentos. O N3E, que será usado para fabricação de alto volume no H2 2023, também será a base para a evolução adicional de 3nm da TSMC.

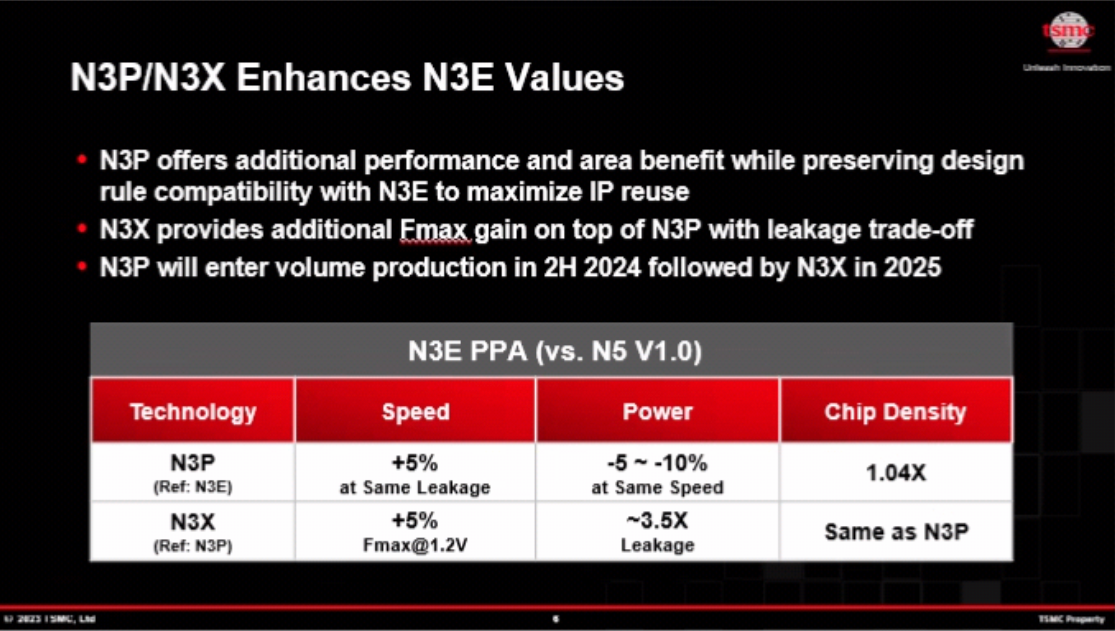

O primeiro passo nessa evolução será o N3P. Essa tecnologia será em grande parte um encolhimento óptico do N3E que apresentará alguns outros refinamentos, permitindo um aumento de desempenho de 5% com o mesmo vazamento, uma redução de energia de 5% a 10% nos mesmos clocks e uma densidade de transistor 4% maior para um ‘ chip misto que consiste em 50% de lógica, 30% de SRAM e 20% de circuitos analógicos.

Como uma redução óptica do N3E, o N3P preserva suas regras de design, permitindo que os projetistas de chips reutilizem o IP do N3E no novo nó. Isso é bastante importante, pois empresas de design de IP como Ansys, Cadence e Synopsys já possuem muitos IPs voltados para chips N3E. Enquanto isso, o encolhimento óptico implica em melhorias de densidade para todos os tipos de transistores e circuitos, incluindo SRAM, um tipo de circuito que tem lutado para encolher nos últimos anos (algo particularmente ruim para projetos modernos intensivos em SRAM). O N3P estará pronto para produção em massa em 2024.

Seguindo o N3P, a TSMC planeja expandir ainda mais sua família N3 e ramificá-la em aplicativos de computação de alto desempenho, como CPUs e GPUs com N3X. Este processo de fabricação é projetado para fornecer frequências pelo menos 5% mais altas em comparação com o N3P e também permitir tensões consideravelmente mais altas, o que aumentará ainda mais os clocks ao custo de um vazamento geral mais alto.

| Linha 0 – Célula 0 | N3X x N3P | N3P x N3E | N3E vs N5 | N3 vs N5 |

| Melhoria de velocidade na mesma potência | +5% Fmáx @ 1,2 V | +5% | +18% | +10% ~ 15% |

| Redução de potência na mesma velocidade | ? | -5% ~ -10% | -32% | -25% ~ -30% |

| Densidade Lógica | mesmo | 1,04x | 1,7x | 1,6x |

| Iniciar HVM | 2025 | H2 2024 | Q2/T3 2023 | H2 2022 |

A TSMC afirma que seu nó N3X pode lidar com pelo menos 1,2 V, uma tensão notavelmente alta para uma tecnologia de fabricação de classe de 3 nm. Isso vem com uma compensação considerável, já que o TSMC prevê um aumento impressionante de 250% no vazamento de energia em comparação com o N3P. Isso destaca que o N3X é adequado principalmente para CPUs HPC e exigirá que os projetistas de chips tenham cuidado ao desenvolver seus chips com consumo de energia de alto desempenho, como CPUs de datacenter e GPUs de computação.

Em termos de densidade do transistor, o N3X corresponderá aos recursos do N3P. A TSMC não especificou se seu N3P e N3E terão regras de design compatíveis, deixando espaço para intrigas sobre se os designs podem ser portados entre os dois nós.